### РАСТР ТЕХНОЛОДЖИ

# Устройство ввода-вывода и обработки телевизионных изображений RT-825

Версия 2.0

Техническое описание

#### ОГЛАВЛЕНИЕ

| 1. ВВЕДЕНИЕ                                                                    | 3     |

|--------------------------------------------------------------------------------|-------|

| 2. ТЕХНИЧЕСКИЕ ХАРАКТЕРИСТИКИ.                                                 | 3     |

| 3. УСТРОЙСТВО И РАБОТА ИЗДЕЛИЯ.                                                | 4     |

| 3.1. ОСНОВНЫЕ ТЕРМИНЫ И СОКРАЩЕНИЯ                                             | 4     |

| 3.2. ОБЩАЯ ФУНКЦИОНАЛЬНАЯ СХЕМА                                                | 5     |

| 3.3. Режимы работы изделия.                                                    | 7     |

| 4. ВЗАИМОДЕЙСТВИЕ ВИДЕОПРОЦЕССОРА С КОМПЬЮТЕРОМ                                | 7     |

| 4.1. РЕГИСТРЫ КОНФИГУРАЦИИ ШИНЫ РСІ                                            | 7     |

| 4.2. ОПЕРАЦИОННЫЕ РЕГИСТРЫ                                                     | 9     |

| 4.2.1. Системный регистр управления                                            | 10    |

| 4.2.2. Регистр управления режимом DMA.                                         | 11    |

| 4.2.3. Регистр адреса DMA.                                                     |       |

| 4.2.4. Регистр счетчика данных DMA                                             | 11    |

| 4.2.5. Регистр событий.                                                        | 11    |

| 4.2.6. Регистр статуса                                                         | 12    |

| 4.2.7. Регистр цифрового ввода-вывода.                                         | 12    |

| 4.2.8. Регистры адреса первого и второго полей кадра, регистр длины строки DMA | 13    |

| 4.2.9. Регистр инициализации динамической памяти.                              | 13    |

| 4.2.10. Регистр управления внутренним буфером памяти                           | 13    |

| 4.2.11. Регистр управления подсистемой ввода изображения.                      | 14    |

| 4.2.12. Регистр управления подсистемой вывода изображения                      | 14    |

| 4.2.13. Регистры усиления и смещения уровня черного входного сигнала, регистр  |       |

| определения амплитуды входного сигнала. Автоматическая настройка яркос         | ги.14 |

| 4.2.14. Регистр коммутации аналоговых входов.                                  | 15    |

| 4.2.15. Регистры настройки формата кадра                                       | 15    |

| 4.2.16. Регистры настройки формата строба статистики                           | 17    |

| 4.2.17. Регистры цифровой обработки входного сигнала                           | 18    |

| 4.3. ОРГАНИЗАЦИЯ И ФУНКЦИОНИРОВАНИЕ ВНУТРЕННЕГО БУФЕРА ПАМЯТИ                  | 18    |

| 4.4. Инициализация видеопроцессора под управлением MS-DOS                      | 20    |

| 4.5 Обмен данными в режиме DMA.                                                |       |

| 4.5.1. Основной старт DMA.                                                     | 21    |

| 4.5.2. Промежуточный старт DMA.                                                |       |

| 4.5.3. Завершение процесса DMA.                                                | 21    |

| 4.6. Ввод изображения в режиме внешнего запуска.                               |       |

| 4.7. Ввод изображения в режиме внешней синхронизации (опция)                   | 22    |

| 5. ПОДГОТОВКА И ПОРЯДОК РАБОТЫ.                                                | 22    |

| 6 ГАРАНТИЙНЫЕ ОБЯЗАТЕЛЬСТВА                                                    | 24    |

#### 1. Введение.

Устройство ввода-вывода и обработки телевизионных изображений RT-825 представляет собой мультиформатный видеопроцессор, предназначенный для высококачественного ввода черно-белого телевизионного изображения в ПК и обработки его в реальном времени. Источником сигнала могут быть ТВ камеры, электронные микроскопы, рентгеновские установки и любые другие устройства, выдающие видеосигнал в различных телевизионных стандартах. Важным свойством видеопроцессора является сочетание таких характеристик, как высокое пространственное разрешение и ввод сигналов без пропуска кадров с высокой частотой их следования (50 Гц и более).

Видеопроцессор имеет 4-канальный входной мультиплексор и видеовыход, позволяющий контролировать на внешнем видеоконтрольном устройстве (ВКУ) ввод сигнала, выводить на ВКУ "замороженный" кадр или последовательность кадров в реальном времени. Для подключения внешних сигналов синхронизации или управляющих и исполнительных устройств имеется четырехразрядный цифровой интерфейс (ТТЛ).

Версия 2.0 видеопроцессора RT-825 на программном и аппаратном уровне совместима с ранее выпускавшимися устройствами RT-821 и имеет по сравнению с ними ряд дополнительных возможностей.

#### 2. Технические характеристики.

#### Видеовход

- 4 программно коммутируемых видеовхода.

- Входное сопротивление: 75 Ом.

- Уровень входного сигнала: от 0.5V pp до 2V pp.

- Полярность синхроимпульсов: отрицательная.

- Синхронизация: внешняя (ТТЛ уровень) или внутренняя.

- Программная регулировка усиления входного сигнала в диапазоне  $\pm 7$  дБ и уровня чёрного в диапазоне  $\pm 0.15$ V; дискретность регулировок 256 градаций; линейность регулировок  $\pm 5\%$ .

- Автоматическая настройка усиления и уровня черного (полное использование динамического диапазона АЦП в автоматическом режиме).

- АЦП: 12 бит, из которых формируются 8/10 битное изображение;

- Частота дискретизации: 6 65 МГц.

- Программируемый формат оцифровки кадра: до **2048 \* 2048 \* 8/10** 2048 строк, 2048 пикселей в строке, 256/1024 градаций серого.

- Дрожание пикселя (jitter): не более  $\pm 2$  нсек.

#### Видеовыход

- Уровень выходного сигнала: 1.0V рр на нагрузке 75 Ом.

- Синхросигнал: формируется программно под любой телевизионный стандарт.

- Уровень и полярность синхроимпульсов: 0.35V, отрицательная.

- Программируемая разрядность ЦАП: 10 бит / 8 бит.

- Частота дискретизации выходного сигнала (пиксельная частота): 12 65 МГц.

- Программируемый формат вывода кадра: до **2048 \* 2048 \* 10** 2048 строк, 2048 пикселей в строке, 1024 градаций серого.

#### Интерфейс и внутренняя память

• Внутренний буфер памяти: 16 Мбайт (4 телевизионных кадра размером до 4 МБайт).

- Интерфейс: 32 битная шина **PCI** MASTER.

- Подключение в стандарте Plug & Play.

- Скорость передачи данных: средняя 60 Мбайт/сек, пиковая 132 Мбайт/сек.

- 4 программируемых цифровых входа/выхода.

#### Конструкция и размеры

- Платы изготовлены на базе ПЛМ фирмы **ALTERA** по технологии **SMD**.

- Габаритные размеры мм 120 \* 86 \* 20.

#### 3. Устройство и работа изделия.

#### 3.1. Основные термины и сокращения.

ВКУ - видеоконтрольное устройство.

*КСИ* – кадровый синхроимпульс.

ССИ – строчный синхроимпульс.

**АЦП** – аналого-цифровой преобразователь.

ADC – (Analog Digital Cconverter) английская аббревиатура АЦП.

**ЦАП** – цифро-аналоговый преобразователь.

**DAC** – (Digital Analog Converter) английская аббревиатура ЦАП.

${\it DMA}$  – (Direct Memory Access) прямой доступ к памяти. Для пересылки изображения из внутренней памяти в память ПЭВМ и обратно, видеопроцессор использует механизм прямого доступа к памяти.

Oкно ввода — прямоугольная область внутри кадра, в пределах которой, будет производиться оцифровка изображения.

Oкно вывода — прямоугольная область внутри кадра, в которую будет записываться выводимое изображение.

*Строб статистики* - прямоугольная область внутри окна ввода, используемая для статистических измерений. Размер строба не может превышать размера окна ввода.

**Фиксация кадра изображения** — оцифровка и запись полного кадра изображения в один из банков внутреннего буфера памяти видеопроцессора.

**DSP** – (Digital Signal Processing) цифровая обработка сигнала.

**Банк памяти** — часть внутренней памяти видеопроцессора объемом 2 МБ для работы с одним кадром изображения. Число банков равно 4.

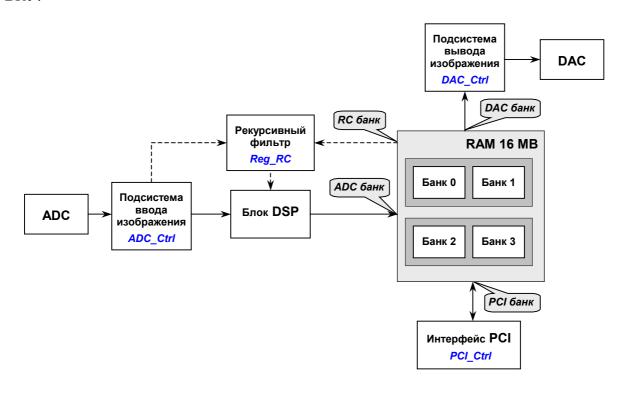

ADC банк – банк, в который на данный момент времени записывается оцифрованное изображение.

**РСІ банк** – банк, из которого в текущий момент времени осуществляется пересылка оцифрованного изображения в память ПЭВМ при вводе кадров или в который осуществляется пересылка изображения из памяти ПЭВМ при выводе кадров на ВКУ

**DAC** банк – банк, используемый для цифро-аналогового преобразования изображения (вывода изображения).

DSP банк — банк, в котором хранится изображение, используемое как второй операнд при DSP обработке сигнала.

**Чередование** (переключение) банков — смена назначения банка памяти. Например, в один момент времени он может использоваться для приема оцифрованного изображения (**ADC** банк), а в следующий момент после переключения, он будет использоваться для обмена с памятью ПЭВМ (**PCI** банк). При переключении банков никакой пересылки данных между ними не происходит.

#### 3.2. Общая функциональная схема.

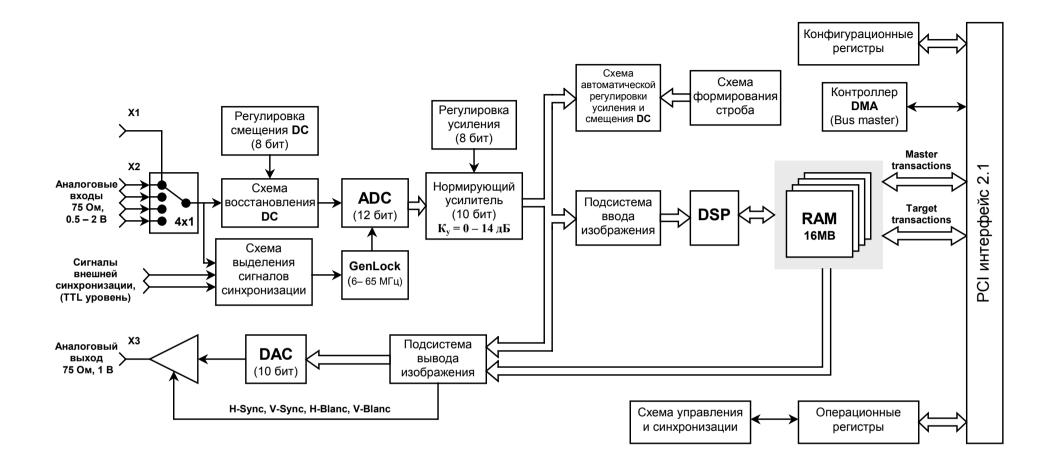

Устройство **RT-825,** функциональная схема которого приведена на рис.1, состоит из следующих основных узлов:

- *4-х канальный видеокоммутатор* осуществляет коммутацию аналоговых входов (время переключения 8 нс);

- *схема восстановления постоянной составляющей (DC)* осуществляет привязку телевизионного сигнала к уровню чёрного;

- *нормирующий усилитель* —преобразует 12-ти разрядный код АЦП в 10-ти разрядный код входных данных в соответствии с требуемым усилением;

- *схемы регулировки смещения постоянной составляющей (DC) и усиления* позволяют автоматически или вручную настраивать яркость и контрастность входного телевизионного изображения (256 градаций);

- *схема выделения сигналов синхронизации* выделяет из входного сигнала строчные и кадровые синхроимпульсы;

- *ADC* 12-ти разрядный аналого-цифровой преобразователь (АЦП);

- *GenLock* широкодиапазонный генератор частоты квантования входного сигнала (пиксельной частоты). Имеет систему фазовой автоподстройки частоты (ФАПЧ) и обеспечивает дрожание пикселя (jitter) не более ± 2 нс;

- *DAC* 10 разрядный цифро-аналоговый преобразователь (ЦАП);

- *подсистема ввода изображения* основной канал ввода. Формирует окно ввода кадров ТВ изображения, осуществляет управление фиксацией изображения во внутреннем буфере памяти;

- *схема формирования строба* формирует прямоугольную область внутри окна ввода, в которой производятся статистические измерения, определяются максимальные и минимальные уровни сигналов;

- *подсистема вывода изображения* формирует окно вывода выходного телевизионного изображения, вырабатывает сигналы синхронизации, осуществляет переключение потоков данных (сквозной канал АЦП-ЦАП / вывод из внутреннего буфера памяти);

- *выходной усилитель* формирует выходной телевизионный сигнал и обеспечивает согласование с 75-омной нагрузкой;

- *схема управления и синхронизации* осуществляет общее управление всеми процессами в устройстве;

- *RAM* 32-х разрядный внутренний буфер памяти (16 МБ). Функционально разделен на 4 банка по 4 МБ;

- *DSP* блок цифровой обработки сигналов реального времени. Выполняет целочисленные операции сложения, вычитания, умножения и деления элементов одного или нескольких изображений, позволяет реализовать различные виды накопления.

- *PCI Interface 2.1, контроллер DMA, конфигурационные и операционные регистры* обеспечивают связь **RT-825** с оперативной памятью компьютера через шину PCI в режимах MASTER и TARGET.

Рис. 1. Функциональная схема видеопроцессора RT-825.

#### 3.3. Режимы работы изделия.

Устройство RT-825 имеет следующие основные режимы работы:

- непрерывный или одиночный ввод кадров телевизионного изображения в оперативную память компьютера с одновременным просмотром его на внешнем видеоконтрольном устройстве (ВКУ);

- вывод на внешнее ВКУ одиночного кадра (без ввода изображения в компьютер);

- вывод на внешнее ВКУ серии ранее введенных кадров в реальном времени или с замедлением (без ввода изображения в компьютер).

#### 4. Взаимодействие видеопроцессора с компьютером.

Устройство RT-825 подключается к ПЭВМ через шину РСІ и использует 32 Кбайт адресного пространства оперативной памяти и одну линию аппаратного прерывания. Для ОС Windows 2000, XP управление видеопроцессором осуществляется драйвером, входящим в комплект поставки, и описанным в документе "Библиотека RT8xxVP. Техническое описание и руководство программиста". При использовании других операционных систем необходимо воспользоваться информацией из разделов 4.1 – 4.6, посвященных подробному описанию внутренней структуры устройства.

#### 4.1. Регистры конфигурации шины PCI.

В соответствии со стандартом шины РСІ, каждое устройство, подключенное к шине, должно иметь конфигурационный заголовок, определяющий порядок взаимодействия устройства с арбитром шины. Конфигурационный заголовок состоит из регистров конфигурации (8-, 16- и 32-разрядных), которые занимают в общей сложности 256 байт. В таблице 1 приведен полный перечень и порядок расположения регистров в конфигурационном заголовке. В таблице 2 дано краткое описание регистров конфигурации, которые поддерживаются видеопроцессором RT-825 (выделены серым цветом в табл.1).

Таблица 1

| Address |                                     | Ву          | te            |                 |

|---------|-------------------------------------|-------------|---------------|-----------------|

|         | 3                                   | 2           | 1             | 0               |

| 00H     | Devid                               | e ID        | Vend          | lor ID          |

| 04H     | Status R                            | Register    | Command       | d Register      |

| 08H     |                                     | Class Code  |               | Revision ID     |

| 0CH     | BIST                                | Header Type | Latency Timer | Cache Line Size |

| 10H     | Base Address Register 0             |             |               |                 |

| 14H     | Base Address Register 1             |             |               |                 |

| 18H     | Base Address Register 2             |             |               |                 |

| 1CH     | Base Address Register 3             |             |               |                 |

| 20H     | Base Address Register 4             |             |               |                 |

| 24H     | Base Address Register 5             |             |               |                 |

| 28H     | Card Bus CIS Pointer                |             |               |                 |

| 2CH     | Subsystem ID Subsystem Vendor ID    |             |               |                 |

| 30H     | Expansion ROM Base Address Register |             |               |                 |

| 34H     | Reserved                            |             |               |                 |

| 38H     | Reserved                            |             |               |                 |

| 3CH    | Maximum Latency | Minimum Grant | Interrupt Pin | Interrupt Line |

|--------|-----------------|---------------|---------------|----------------|

| 40HFFH |                 | Rese          | erved         |                |

#### Таблица 2

| Смещение<br>адреса<br>регистра | Адресный<br>диапазон<br>регистра | Чтение /<br>запись | Начальное<br>значение | Название<br>регистра       | Описание регистра                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|----------------------------------|--------------------|-----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h                            | 00h-01h                          | Чтение             | 5254h                 | Vendor ID                  | Идентификатор производителя устройства – фирма РАСТР ТЕХНОЛОДЖИ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 02h                            | 02h-03h                          | Чтение             | 0821h                 | Device ID                  | Идентификатор типа устройства – эмуляция устройства RT-821                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 04h                            | 04h-05h                          | Чтение/<br>запись  | 0000h                 | Command                    | Обеспечивает подключение устройства к шине PCI:  бит 0 – не используется; бит 1 – разрешает доступ к памяти; бит 2 – разрешает режим MASTER; бить 53 – не используются; бит 6 – разрешает выдачу сигнала PERR на шине PCI при обнаружении ошибки четности данных; бит 7 – не используется; бит 8 – разрешает выдачу сигнала SERR на шине PCI при обнаружении ошибки четности адреса (должен быть установлен бит 6); биты 159 – не используются.                                                                                                                                                                                                                                                                                                                                              |

| 06h                            | 06h-07h                          | Чтение/<br>запись  | 0400h                 | Status                     | Содержит информацию о некоторых режимах и результатах работы устройства на шине PCI (для процесса начальной инициализации устройства этот регистр не используется).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08h                            | 08h-08h                          | Чтение             | 02h                   | Revision ID                | Идентификатор номера версии исполнения устройства                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 09h                            | 09h-0Bh                          | Чтение             | 040000h               | Class Code                 | Содержит информацию о принадлежности данного устройства к определенному классу устройств (плата RT825 принадлежит к классу устройств Multimedia).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0Dh                            | 0Dh-0Dh                          | Чтение/<br>запись  | 00h                   | Latency Timer              | Используется в режиме MASTER для определения длительности непрерывной передачи одной порции данных на шине PCI.  Биты 20 – не используются и равны 0;  Биты 73 – определяют длительность непрерывной порции данных в тактах шины PCI, умноженных на 8 (максимальное число – 0, что соответствует 256-ти тактам).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0Eh                            | 0Eh-0Eh                          | Чтение             | 00h                   | Header Type                | Указывает на то, что RT-825 не является многофункциональным PCI устройством (см. спецификацию шины).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10h                            | 10h-13h                          | Чтение/<br>запись  | 00000000h             | Base Address<br>Register 0 | Первый базовый адресный регистр. Он определяет диапазон адресов памяти, занимаемых устройством, и место его расположения в общем пространстве адресов памяти. Биты 140 используются только для чтения, а биты 3115 – для чтения и записи. Бит 0 – равен 0 и указывает на принадлежность базового адреса к пространству адресов памяти; Биты 21 – равны 0, что определяет возможность расположения занимаемого устройством диапазона адресов памяти в любом месте 32-х разрядного адресного пространства; Бит 3 – равен 0 и указывает на то, что режим "Prefetchable" устройством не поддерживается (см. спецификацию шины PCI); Биты 144 – равны 0 и указывают на то, что диапазон адресов памяти, занимаемого устройством, составляет 32 Кбайт; Биты 3115 – определяют базовый адрес в 32-х |

| Смещение<br>адреса<br>регистра | Адресный<br>диапазон<br>регистра | Чтение /<br>запись | Начальное<br>значение | Название<br>регистра | Описание регистра                                                                                                                                                                                                                      |

|--------------------------------|----------------------------------|--------------------|-----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                  |                    |                       |                      | разрядном адресном пространстве памяти.                                                                                                                                                                                                |

| 3Ch                            | 3Ch-3Ch                          | Чтение/<br>запись  | FFh                   | Interrupt Line       | Определяет номер прерывания (от 0 до 15), используемого устройством. Значение FFh говорит о том, что прерывание по умолчанию не используется.                                                                                          |

| 3Dh                            | 3Dh-3Dh                          | Чтение             | 01h                   | Interrupt Pin        | Информирует о том, какая аппаратная линия на шине PCI задействована под прерывание. Значение 01h говорит о том, что под прерывание задействована линия INTA#.                                                                          |

| 3Eh                            | 3Eh-3Eh                          | Чтение             | 10h                   | Minimum<br>Grant     | Используется только как информационный и сообщает арбитру шины о предполагаемой длительности непрерывной порции данных, передаваемых через шину. Значение длительности выражено в 250-ти наносекундных отрезках (10h x 250нс = 4 мкс). |

| 3Fh                            | 3Fh-3Fh                          | Чтение             | 00h                   | Maximum<br>Latency   | Используется только как информационный и сообщает арбитру шины о том, как часто устройство предполагает задействовать шину для передачи данных. Значение 00h говорит о том, что требования к этому параметру не определены.            |

#### 4.2. Операционные регистры.

После проведения процесса инициализации видеопроцессору RT-825 будет выделено 32 Кбайт в адресном пространстве памяти компьютера. Функционально это пространство состоит из двух частей: нижние 16 Кбайт занимают управляющие *операционные регистры*, а верхние 16 Кбайт являются окном, через которое происходит обмен данными между внутренним буфером памяти RT-825 и оперативной памятью компьютера. Следует отметить, что это окно используется только в режиме TARGET (в режиме MASTER данное окно не используется).

Физический адрес первого операционного регистра определяется значением, указанным в первом базовом адресном регистре конфигурационного заголовка. Например, если базовый адрес равен 000D0000h, то операционные регистры займут область памяти 000D0000 - 000D3FFF, а окно обмена данными – область с 000D4000h по 000D7FFFh.

Операционные регистры, имеющие разрядность более 16 бит, программируются только с помощью 32-х разрядных операций чтения/записи (не допускается запись, например, сначала младших, а затем старших 16 бит).

В таблице 3 приведен перечень всех операционных регистров устройства.

Таблица 3

| Смещение<br>адреса<br>регистра | Направление<br>операции<br>(чтение/запись) | Аббревиатура регистра | Описание регистра                 |

|--------------------------------|--------------------------------------------|-----------------------|-----------------------------------|

| 00H                            | запись                                     | Syst_Ctrl             | Системный регистр управления      |

| 04H                            | запись                                     | DMA_Ctrl              | Регистр управления режимом DMA    |

| 08H                            | запись                                     | DMA_Addr              | Регистр адреса DMA                |

| 0CH                            | запись                                     | DMA_Byte              | Регистр счетчика данных DMA       |

| 10H                            | чтение                                     | Reg_Events            | Регистр событий                   |

| 14H                            | чтение                                     | Reg_Stat              | Регистр статуса                   |

| 18H                            | запись/чтение                              | Reg_DIO               | Регистр цифрового ввода-вывода    |

| 20H                            | запись                                     | DMA_Line              | Регистр длины строки DMA          |

| 24H                            | запись                                     | Mem_Addr              | Регистр адреса первого поля кадра |

| Смещение<br>адреса<br>регистра | Направление<br>операции<br>(чтение/запись) | Аббревиатура регистра | Описание регистра                                       |

|--------------------------------|--------------------------------------------|-----------------------|---------------------------------------------------------|

| 28H                            | запись                                     | Mem_Addr1             | Регистр адреса второго поля кадра                       |

| 34H                            | запись                                     | Mem_Init              | Регистр инициализации динамической памяти               |

| 38H                            | запись                                     | PLL_Ctrl              | Регистр управления внутренним буфером памяти            |

| 3CH                            | запись                                     | ADC_Ctrl              | Регистр управления подсистемой ввода изображения        |

| 40H                            | Запись                                     | DAC_Ctrl              | Регистр управления подсистемой вывода изображения       |

| 44H                            | запись                                     | MUX_A                 | Регистр коммутации аналоговых входов                    |

| 98H                            | запись                                     | ADC_Ctrl              | Регистр аналогового смещения уровня черного             |

| 48H                            | запись                                     | Reg_Level             | Регистр цифрового смещения уровня черного               |

| 4CH                            | запись                                     | Reg_Gain              | Регистр усиления входного сигнала                       |

| 50H                            | чтение                                     | ADC_MinMax            | Регистр определения амплитуды входного сигнала          |

|                                |                                            | Регистры настройк     | и формата кадра                                         |

| 54H                            | запись                                     | PLL_Ctrl              | Регистр настройки частоты оцифровки                     |

| 58H                            | запись                                     | Len_Line_All          | Полная длина строки (количество пикселей)               |

| 5CH                            | запись                                     | Beg_Line_Act          | Начало активной части строки (номер пикселя)            |

| 60H                            | запись                                     | Len_Line_Act          | Длина активной части строки (количество пикселей)       |

| 64H                            | запись                                     | Numb_Line_Act         | Начало активной части первого поля кадра (номер строки) |

| 68H                            | запись                                     | Beg_Field2_Act        | Начало активной части второго поля кадра (номер строки) |

| 6CH                            | запись                                     | Numb_Line_Act         | Число активных строк кадра                              |

| 70H                            | запись                                     | Numb_Line_All         | Число всех строк кадра                                  |

| 84H                            | запись                                     | PLL_                  | Период строчной частоты (в микросекундах)               |

|                                | Pea                                        | гистры настройки форм | ата строба статистики                                   |

| ACH                            | запись                                     | Strob_L               | Левая граница строба внутри кадра                       |

| ВОН                            | запись                                     | Strob_R               | Правая граница строба внутри кадра                      |

| B4H                            | запись                                     | Strob_U               | Верхняя граница строба внутри кадра                     |

| ВСН                            | запись                                     | Strob_D               | Нижняя граница строба внутри кадра                      |

|                                |                                            | Регистры цифровой с   | обработки сигнала                                       |

| 94H                            | запись                                     | Reg_Accum             | Регистр управления накоплением входного сигнала         |

| D4H                            | запись                                     | Reg_RC                | Регистр управления рекурсивным фильтром (опция)         |

#### 4.2.1. Системный регистр управления.

С помощью регистра **Syst\_Ctrl** задается маска прерываний по различным событиям и осуществляется настройка цифровых линий ввода-вывода.

Установкой в 1 битов D8..D1 регистра **Syst\_Ctrl** разрешается фиксация соответствующих событий в регистре **Reg\_Events**. Бит D0 разрешает генерацию прерываний от устройства RT-825 при наступлении этих событий.

| Биты | Описание                                                                                |

|------|-----------------------------------------------------------------------------------------|

| 0    | Общее разрешение прерываний                                                             |

| 1    | Разрешение прерывания при завершении DMA                                                |

| 2    | Разрешение прерывания от входных кадровых синхроимпульсов                               |

| 3    | Разрешение прерывания от выходных кадровых синхроимпульсов                              |

| 4    | Разрешение прерывания при пропадании входного сигнала                                   |

| 5    | Разрешение прерывания по изменению логического состояния на цифровой линии <b>I/O-1</b> |

| Биты | Описание                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | Разрешение прерывания по изменению логического состояния на цифровой линии I/O-2                                                                                            |

| 7    | Разрешение прерывания по изменению логического состояния на цифровой линии I/O-3                                                                                            |

| 8    | Разрешение прерывания по изменению логического состояния на цифровой линии I/О-4                                                                                            |

| 129  | Выбор направления цифровых линий <b>I/O-4 I/O-1</b> 0 - ввод с внешнего разъема  1 - вывод логических ТТЛ уровней на внешний разъем через биты D3D0 регистра <b>Reg_DIO</b> |

| 3113 | Не используется                                                                                                                                                             |

#### 4.2.2. Регистр управления режимом DMA.

Регистр **DMA\_Ctrl** организует порядок обмена данными через интерфейс PCI в режиме MASTER.

| Биты | Описание                                                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Формат данных при передаче в режиме двух байт на пиксель:  0 - 10-ти разрядный формат (значащие биты – D9D0)  1 - 16-ти разрядный формат (значащие биты – D15D0)                                     |

| 1    | Принудительный останов режима DMA 0 - DMA проходит в обычном режиме 1 - режим DMA остановлен                                                                                                         |

| 2    | Разрядность передаваемых данных 0 - один байт на пиксель (8 бит) 1 - два байта на пиксель (10/16 бит)                                                                                                |

| 3    | Направление передачи данных через интерфейс PCI:  0 - данные записываются во внутренний буфер видеопроцессора  1 - данные читаются из внутреннего буфера видеопроцессора                             |

| 4    | Чтение/запись чересстрочного изображения  0 - последовательное (прогрессивное) чтение/запись данных  1 - чтение/запись данных через строку (длина строки в пикселях указывается в регистре DMA_Line) |

| 5    | Чтение/запись данных с вертикальным отражением 0 - чтение/запись данных от верхней строки к нижней 1 - чтение/запись данных от нижней строки к верхней (Vertical Flip)                               |

| 316  | Не используются                                                                                                                                                                                      |

#### 4.2.3. Регистр адреса DMA.

В регистр **DMA\_Addr** записывается 32-х разрядный адрес, указывающий на начало области оперативной памяти компьютера, с которой будет организован обмен данными при выполнении DMA. Операция записи в регистр **DMA Addr** дает также старт процессу DMA.

#### 4.2.4. Регистр счетчика данных DMA.

Регистр **DMA\_Byte** является 21-разрядным счетчиком количества переданных байт в ходе выполнения DMA. За один цикл DMA можно передать до 1024 КБайт данных в формате один байт на пиксель или до 2048 Кбайт данных в формате два байта на пиксель. Значение количества байт, записываемое в регистр, должно быть кратно 16.

#### 4.2.5. Регистр событий.

В регистре **Reg\_Events** фиксируется информация о событиях, вызвавших прерывание. В момент наступления одного из разрешенных событий устанавливается в 1 соответствую-

щий бит регистра **Reg\_Events** и выдается прерывание. При чтении регистра все установленные в 1 биты сбрасываются в 0, а прерывание снимается.

<u>Важно! При обработке прерываний чтение регистра **Reg\_Events** является обязательным условием.</u>

| Биты | Описание                                                                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Завершение процесса DMA. Бит устанавливается в "1", когда счетчик количества переданных байт достигнет нуля, что свидетельствует об успешном завершении процесса DMA. |

| 1    | Ошибка во время выполнения DMA                                                                                                                                        |

| 2    | Появление кадрового синхроимпульса во входном сигнале                                                                                                                 |

| 3    | Появление кадрового синхроимпульса в выходном сигнале                                                                                                                 |

| 4    | Пропадание входного сигнала                                                                                                                                           |

| 5    | Изменение логического состояния одного либо нескольких цифровых входов                                                                                                |

| 316  | Не используются                                                                                                                                                       |

#### 4.2.6. Регистр статуса.

В регистре статуса **Reg\_Stat** отражается информация о состоянии устройства и происходящих в нем процессах.

| Биты | Описание                                                                                                                                                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Окончание фиксации кадра во внутреннем буфере памяти. Бит сбрасывается в "0" при программировании режима фиксации кадра и устанавливается в "1" в конце ввода одного кадра в режиме без накопления или последнего введенного кадра в режиме с накоплением                     |

|      | 0 – процесс фиксации кадра не закончен<br>1 – процесс фиксации кадра закончен                                                                                                                                                                                                 |

| 1    | Фиксация телевизионного кадра во внутреннем буфере памяти. Бит устанавливается в "1" с началом ввода кадра и сбрасывается в "0" в конце ввода кадра в режиме без накопления или последнего введенного кадра в режиме с накоплением                                            |

|      | 0 – процесс фиксации еще не начат или уже закончен<br>1 – идет процесс фиксации кадра ТВ сигнала                                                                                                                                                                              |

| 2    | Кадровый синхроимпульс во входном сигнале. Бит устанавливается в "1", когда во входном сигнале присутствуют кадровые синхроимпульсы полей кадра.                                                                                                                              |

| 3    | Номер (или четность) поля текущего кадра входного телевизионного сигнала  0 – первое поле кадра  1 – второе поле кадра                                                                                                                                                        |

| 4    | Отсутствие входного телевизионного сигнала  0 – сигнал на входе присутствует  1 – сигнала на входе нет                                                                                                                                                                        |

| 5    | Вывод очередного кадра изображения. Бит устанавливается в "1" в начале и сбрасывается в "0" в конце вывода полного кадра. Он может использоваться для синхронизации смены банков памяти с записанными в них телевизионными кадрами при выводе изображения на внешний монитор. |

| 6    | Процесс DMA активен. Бит устанавливается в "1" при записи адреса в регистр <b>DMA_Addr</b> и сбрасывается в "0" при завершении либо остановке процесса DMA.                                                                                                                   |

| 317  | Не используются                                                                                                                                                                                                                                                               |

#### 4.2.7. Регистр цифрового ввода-вывода.

Регистр **Reg\_DIO** осуществляет связь видеопроцессора с внешним устройством посредством сигналов в уровнях ТТЛ логики через соответствующие цифровые линии. Направление передачи сигналов для каждого цифрового входа-выхода устанавливается битами D12..D9 регистра **Syst\_Ctrl.** Линия **I/O-2** через резистор 1 кОм подключена к +5В и может использоваться для внешнего запуска с помощью кнопки (замыканием на корпус).

| Биты | Описание                                                           |

|------|--------------------------------------------------------------------|

| 30   | Входные/выходные цифровые линии <b>I/O-4 I/O-1</b> (см. таблицу 3) |

| 318  | Не используются                                                    |

#### 4.2.8. Регистры адреса первого и второго полей кадра, регистр длины строки DMA.

Регистры **Mem\_Addr** и **Mem\_Addr1** (21 бит) являются указателями на текущий адрес памяти в банке внутреннего буфера видеопроцессора для первого и второго полей кадра (номер банка определяется битами D[1..0] регистра **PCI\_Ctrl**). При выполнении DMA эти указатели смещаются в соответствии с количеством переданных байт в каждом поле.

При прогрессивном способе обмена данными в регистры **Mem\_Addr** и **Mem\_Addr1** записывается адрес первой (при чтении/записи строк сверху вниз) или последней (при чтении/записи строк снизу вверх) строки окна ввода кадра. Размер и положение окна ввода определяется регистрами входного/выходного формата кадра (4.2.15).

При чересстрочном способе обмена данными и чтении/записи строк сверху вниз в регистр **Mem\_Addr** записывается адрес первой строки первого поля окна ввода кадра, а в регистр **Mem\_Addr1** – адрес первой строки второго поля окна ввода.

При чересстрочном способе обмена данными и чтении/записи строк снизу вверх (Vertical Flip) в регистр **Mem\_Addr** записывается адрес последней строки второго поля окна ввода кадра, а в регистр **Mem\_Addr1** – адрес последней строки первого поля.

Если передается не все окно ввода, то в регистры **Mem\_Addr** и **Mem\_Addr1** записываются необходимые смещения от начала (или конца) полей кадра. В этом случае значение регистра **Mem Addr1** можно вычислить по формуле:

```

[Mem_Addr] + [DMA_Line] * [Numb_Line_Act + 1] / 2 — для 8-разрядных данных;

[Mem_Addr] + [DMA_Line] * [Numb_Line_Act + 1] — для 16-разрядных данных.

```

Регистр **DMA\_Line** (11 бит) определяет длину строки кадра в пикселях, передаваемого через шину РСІ.

Значения, записываемые в регистры Mem\_Addr, Mem\_Addr1 и DMA\_Line, должны быть кратны 16.

#### 4.2.9. Регистр инициализации динамической памяти.

Регистр **Mem\_Init** используется для инициализации динамической памяти RT825. При старте драйвера или программы в этот регистр записывается значение 0.

#### 4.2.10. Регистр управления внутренним буфером памяти.

Регистр **PCI\_Ctrl** осуществляет выбор PCI банка, а также организует порядок обмена данными с внутренним буфером памяти в режиме TARGET (см. раздел 'Организация внутреннего буфера памяти').

| Биты | Описание                                                       |                                                                   |  |  |  |  |  |  |

|------|----------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| 10   | Выбор номера банка для обмена данными через PCI (выбор PCI бан | Выбор номера банка для обмена данными через PCI (выбор PCI банка) |  |  |  |  |  |  |

| 2    | Не используется                                                |                                                                   |  |  |  |  |  |  |

| 93   | Номер окна в PCI банке (только для режима TARGET)              |                                                                   |  |  |  |  |  |  |

|      | D9 D8 D7 D6 D5 D4 D3 Номер окна                                |                                                                   |  |  |  |  |  |  |

|      | 0 0 0 0 0 0 0                                                  |                                                                   |  |  |  |  |  |  |

|      | 0 0 0 0 0 1 1                                                  |                                                                   |  |  |  |  |  |  |

|      | 0 0 0 0 1 0 2                                                  |                                                                   |  |  |  |  |  |  |

|      |                                                                |                                                                   |  |  |  |  |  |  |

| Биты |                 |   |   |   |   |   |   | Описание |  |

|------|-----------------|---|---|---|---|---|---|----------|--|

|      | 1               | 1 | 1 | 1 | 1 | 1 | 1 | 127      |  |

| 319  | Не используются |   |   |   |   |   |   |          |  |

#### 4.2.11. Регистр управления подсистемой ввода изображения.

Регистр **ADC\_Ctrl** осуществляет управление фиксацией входного ТВ изображения во внутреннем буфере памяти видеопроцессора.

| Биты | Описание                                                                                     |

|------|----------------------------------------------------------------------------------------------|

| 10   | Выбор номера банка для ввода ТВ сигнала (ADC банка)                                          |

| 42   | Не используются                                                                              |

| 5    | Включение прорисовки границ строба статистики                                                |

| 76   | Не используются                                                                              |

| 8    | Включение режима фиксации кадра. Бит автоматически сбрасывается по окончании фиксации кадра. |

| 319  | Не используются                                                                              |

#### 4.2.12. Регистр управления подсистемой вывода изображения.

Регистр **DAC\_Ctrl** управляет выводом ТВ изображения из внутреннего буфера памяти видеопроцессора на внешний монитор.

| Биты | Описание                                                                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10   | Выбор номера банка для вывода ТВ сигнала (DAC банка)                                                                                                                           |

| 32   | Не используются                                                                                                                                                                |

| 4    | Включение режима вывода одного полукадра. В этом режиме при выводе на экран монитора второе поле кадра замещается первым (полезно при просмотре динамических изображений)      |

| 5    | Включение режима просмотра входного изображения – сквозного канала АЦП – ЦАП. <i>При вводе ТВ сигнала этот бит должен быть обязательно установлен в 1</i>                      |

|      | 0 – вывод изображения на внешний монитор из внутреннего буфера памяти (ввод ТВ сигнала невозможен) 1 – на внешний монитор сигнал поступает непосредственно с аналогового входа |

| 6    | Включение гашения выходного сигнала (без обнуления данных во внутреннем буфере)                                                                                                |

| 317  | Не используются                                                                                                                                                                |

## 4.2.13. Регистры усиления и смещения уровня черного входного сигнала, регистр определения амплитуды входного сигнала. Автоматическая настройка яркости.

С помощью 8-разрядных регистров **Reg\_Gain** и **Reg\_Level** осуществляется настройка контрастности и яркости вводимого изображения. Регистр **Reg\_Gain** производит регулировку усиления видеосигнала и определяет максимальный уровень белого. Регистр **Reg\_Level** задает смещение постоянной составляющей видеосигнала и используется для настройки уровня черного.

Регистр определения амплитуды входного сигнала **ADC\_MinMax** позволяет за время ввода кадра определить минимальное (ADC\_Min) и максимальное (ADC\_Max) 8/12-ти битовые значения входного сигнала внутри строба статистики. Эти значения в дальнейшем могут быть использованы для корректировки содержимого регистров **Reg\_Gain** и **Reg\_Level** с целью оптимальной настройки яркости и контрастности вводимого изображения.

| Биты | Описание                                                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 70   | Старшие 8 бит минимального уровня входного сигнала, зафиксированного во время ввода последнего кадра.                                   |

| 158  | Старшие 8 бит максимального уровня входного сигнала, зафиксированного во время ввода последнего кадра.                                  |

| 1916 | Младшие 4 бита минимального уровня входного сигнала. Совместно с битами D7D0 используются для формирования 12-ти разрядного значения.   |

| 2320 | Младшие 4 бита максимального уровня входного сигнала. Совместно с битами D15D8 используются для формирования 12-ти разрядного значения. |

| 3124 | Не используются                                                                                                                         |

**Автоматическая регулировка яркости и контрастности** вводимого изображения заключается в нахождении таких значений регистров **Reg\_Gain** и **Reg\_Level**, при которых входной видеосигнал растягивается на весь диапазон АЦП. При этом сигнал оценивается лишь в выбранной зоне интереса — в стробе статистики, который может иметь размер от нескольких пикселей до полного кадра. Алгоритм автоматической регулировки состоит из двух шагов.

Сначала при минимальном усилении ([Reg\_Gain] = 0) методом последовательного приближения определяется оптимальное значение регистра Reg\_Level, соответствующее минимальному значению ADC\_Min исследуемого сигнала в выбранной зоне интереса (в стробе статистики). Вторым шагом рассчитывается оптимальный коэффициент усиления, соответствующий максимально допустимому уровню белого. Коэффициент усиления линейно регулируется от 1 до 5 и пересчитывается в значение регистра Reg\_Gain по следующей формуле:

$$[Reg\_Gain] = 64 * (K - 1)$$

где К – коэффициент цифрового усиления, равный

K = 256 / (ADC\_Max +1), при использовании 8-битового значения ADC\_Max или

K = 4096 / (ADC Max + 1), при использовании 12-битового значения ADC Max.

Значение регистра **Reg** Gain не должно превышать 255.

#### 4.2.14. Регистр коммутации аналоговых входов.

Регистр MUX\_A осуществляет подключение одного из четырех аналоговых входов.

| Биты | Описание                                                                              |

|------|---------------------------------------------------------------------------------------|

| 10   | Выбор аналогового входа                                                               |

|      | D1 D0     Номер входа       0 0     0       0 1     1       1 0     2       1 1     3 |

| 312  | Не используются                                                                       |

#### 4.2.15. Регистры настройки формата кадра.

| Аббревиатура<br>регистра | Описание регистра                                                         | Значение для<br>сигнала стандарта<br>ССІR |

|--------------------------|---------------------------------------------------------------------------|-------------------------------------------|

| Len_Line_All             | Общая длина строки (количество пикселей в строке)                         | 943                                       |

| Beg_Line_Act             | Количество пикселей от переднего фронта синхроимпульса до начала активной | 159                                       |

| Аббревиатура<br>регистра | Описание регистра                                                      | Значение для<br>сигнала стандарта<br>CCIR |

|--------------------------|------------------------------------------------------------------------|-------------------------------------------|

|                          | части строки                                                           |                                           |

| Len_Line_Act             | Длина активной части строки (в пикселах)                               | 767                                       |

| Beg_Field1_Act           | Номер строки, соответствующей началу активной части первого поля кадра | 21                                        |

| Beg_Field2_Act           | Номер строки, соответствующей началу активной части второго поля кадра | 334                                       |

| Numb_Line_Act            | Число активных строк кадра                                             | 575                                       |

| Numb_Line_All            | Число всех строк кадра                                                 | 624                                       |

| T_Line                   | Период строчной частоты (в тактах опорной 59 МГц частоты)              | 3775                                      |

| PLL_Ctrl                 | Настройка режимов синхронизации и генератора пиксельной частоты        | 200H                                      |

В зависимости от значения бита D5 регистра **DAC\_Ctrl** регистры формата кадра определяют либо формат оцифровки кадра при вводе ТВ изображения (D5=1), либо формат кадра при выводе изображения на внешний монитор (D5=0).

В регистры Len\_Line\_All, Beg\_Line\_Act, Len\_Line\_Act, Beg\_Field1\_Act, Beg\_Field2\_Act, Numb\_Line\_Act, Numb\_Line\_All записываются значения на единицу меньше фактических значений.

Значение регистра **Beg\_Field2\_Act** зависит от типа развертки видеосигнала и начала активной части первого поля кадра. Для сигнала с чересстрочной разверткой значение регистра **Beg Field2 Act** вычисляется по формуле:

[Beg Field2 Act] = [Numb Line All]

$$/2 + [Beg Field1 Act] + 1$$

Для сигнала с прогрессивной разверткой в регистр **Beg\_Field2\_Act** записывается то же значение, что и в регистр **Beg\_Field1 Act**.

В регистр **T\_Line** записывается значение периода строчной частоты сигнала в тактах опорной частоты 59 М $\Gamma$ ц:

$$[T_Line] = T * 59 - 1,$$

где  $T - период строчной частоты в микросекундах$

Все перечисленные регистры имеют разрядность 11 бит (максимальное значение 2047). Однако при выборе формата кадра необходимо учитывать следующие ограничения:

- длина активной части строки должна быть кратна 16;

- максимальный размер окна ввода, равный произведению [Len\_Line\_Act] \* [Numb\_Line\_Act], должен быть не более 2МБ.

Регистр **PLL\_Ctrl** служит для настройки и переключения режимов синхронизации, а также для настойки  $\Phi$ AПЧ генератора пиксельной частоты. Значения битов регистра в зависимости от периода строчной частоты входного сигнала в микросекундах — Т (регистр **T\_Line**), общей длины строки в пикселях — L (регистр **Len\_Line\_All**), и их отношения — L/T, указаны в таблице.

| Биты | Т    | L/T  | Значение                                                                                                                                                                                                                                                                                                          |

|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70   | 1069 | -    | Настройка режима внутренней синхронизации:  0 - значение по умолчанию;  1159 - ручная настройка режима синхронизации. Используется, если значение по умолчанию не обеспечивает устойчивого изображения. Если при переборе всех значений синхронизация не настраивается, можно использовать бит 13 этого регистра. |

|      |      | >22  | 0                                                                                                                                                                                                                                                                                                                 |

| 98   | 5869 | 1222 | 1                                                                                                                                                                                                                                                                                                                 |

|      |      | 812  | 2                                                                                                                                                                                                                                                                                                                 |

|      |      | < 8  | 3                                                                                                                                                                                                                                                                                                                 |

|      |      | >25  | 0                                                                                                                                                                                                                                                                                                                 |

| Биты | Т    | L/T  | Значение                                                                                                                                                                                                                                                                    |

|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 3457 | 1325 | 1                                                                                                                                                                                                                                                                           |

|      |      | 713  | 2                                                                                                                                                                                                                                                                           |

|      |      | < 7  | 3                                                                                                                                                                                                                                                                           |

|      |      | >15  | 0                                                                                                                                                                                                                                                                           |

|      | 2934 | 815  | 1                                                                                                                                                                                                                                                                           |

|      | 2954 | 48   | 2                                                                                                                                                                                                                                                                           |

|      |      | < 4  | 3                                                                                                                                                                                                                                                                           |

|      |      | >10  | 0                                                                                                                                                                                                                                                                           |

|      | 1029 | 510  | 1                                                                                                                                                                                                                                                                           |

|      | 1029 | 35   | 2                                                                                                                                                                                                                                                                           |

|      |      | < 3  | 3                                                                                                                                                                                                                                                                           |

| 10   | _    | _    | Выбор способа синхронизации при выводе видеосигнала:                                                                                                                                                                                                                        |

|      |      |      | 0 - синхроимпульсы формируются внутренним генератором 1 - синхроимпульсы выделяются из входного сигнала. В этом случае при переключении режимов ввода/вывода изображение на ВКУ не подергивается.                                                                           |

| 11   | _    | -    | Выбор режима синхронизации:<br>0 – режим внутренней синхронизации<br>1 – режим внешней синхронизации                                                                                                                                                                        |

| 12   | -    | -    | Включение помехоподавляющего фильтра в цепи выделения сигналов синхронизации:  0 - используется при стабильном входном сигнале 1 - используется при неустойчивой синхронизации                                                                                              |

| 13   | -    | -    | Включение альтернативного метода выделения строчных синхроимпульсов. Используется для некоторых видеосигналов с нестандартной структурой синхросмеси.  0 - альтернативный метод отключен. 1 - альтернативный метод включен. Невозможно включение помехоподавляющего фильтра |

| 3114 | _    | _    | Не используются                                                                                                                                                                                                                                                             |

#### 4.2.16. Регистры настройки формата строба статистики.

| Аббревиатура<br>регистра | Описание регистра                                                                   |

|--------------------------|-------------------------------------------------------------------------------------|

| Strob_L                  | Количество пикселей от левой границы кадра до левой границы строба                  |

| Strob_R                  | Количество пикселей от левой границы кадра до правой границы строба                 |

| Strob_U                  | Количество пикселей от верхней границы первого поля кадра до верхней границы строба |

| Strob_D                  | Количество пикселей от верхней границы первого поля кадра до нижней границы строба  |

Строб статистики используется для задания некоторой прямоугольной области внутри кадра, где будут вычисляться минимальные и максимальные значения уровня входного сигнала. Размер и положение строба может быть произвольным, но не выходящим за границы кадра при прогрессивной развертке или за границы первого поля кадра при чересстрочной развертке. Это означает, что для сигнала с чересстрочной разверткой в регистры **Strob\_U** и **Strob\_D** записываются значения в два раза меньшие фактических, поскольку во втором поле кадра строб будет повторен с теми же параметрами что и в первом.

Границы строба при вводе изображения можно прорисовать, включив бит D5 в регистре **ADC\_Ctrl.**

При любом изменении формата кадра размер строба автоматически становится равным размеру кадра. Поэтому, для восстановления прежних границ строба потребуется повторно запрограммировать регистры формата строба, не забыв при этом проверить значения параметров на допустимый диапазон.

#### 4.2.17. Регистры цифровой обработки входного сигнала.

Регистр **Reg\_Accum** осуществляет управление *режимом накопления кадров* входного ТВ сигнала. Если задана какая-либо функция цифровой обработки, то она выполняется в конечной стадии режима накопления при вводе последнего кадра.

| Биты | Описание                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 10   | Выбор количества накапливаемых кадров:  розината разрания в разра |  |  |  |  |  |  |  |  |